Abstract

The geometry of fracture associated with the propagation of cracks originating at the edges of (001) oriented, 200 mm diameter silicon wafers has been investigated under two regimes of high temperature processing. Under spike annealing, fracture did not occur on low index planes and all except one wafer exhibited crack patterns that started initially to run radially, but after a distance of typically 20–30 mm, turned and ran almost tangentially. Wafers subjected to plateau annealing, with a 60 s dwell time at high temperature, predominantly fractured through radial cracks running along \(\langle 110\rangle \) directions. X-ray diffraction imaging reveals substantial slip in all wafers subjected to plateau annealing. We demonstrate using finite element (FE) modelling that the change in fracture geometry is associated with this plastic deformation, which changes the stress distribution during the cooling phase of the rapid thermal annealing cycle. FE simulations without plastic relaxation show that the radial component of the thermal stress distribution is compressive in the centre of the wafer, causing the crack to run tangentially. Simulations incorporating temperature dependent plasticity showed that the equivalent stress becomes tensile when the plateau anneal allows time for significant plastic relaxation, permitting the crack to continue propagating linearly.

Similar content being viewed by others

1 Introduction

Wafer breakage during high temperature processing is a multi-million dollar problem in semiconductor manufacturing lines, the prime cost being in loss of product during the time taken to stop the line, recover the broken wafer, clean and restart the affected tool. Although Chen et al. (2009, 2010) found a statistical correlation between wafer failure during processing and the geometry of the edge bevel shape, the prime origin of these failures appears to be cracks at the wafer edge associated with misaligned handling tools. Rather than rely on statistical approaches (Cook 2006; Brun and Melkote 2009), we have developed an X-ray diffraction imaging (XRDI) technique for assessing the probability that individual cracks will propagate (Tanner et al. 2012). This methodology underpins commercial XRDI products now on the market.

The fracture mode has been a matter of question as it has been noted that (001) oriented wafers sometimes fracture quasi-circumferentially and sometimes parallel to low index \(\langle 110\rangle \) directions. When failure occurs by the former mode during high temperature processing, the disruption can be substantial due to small fragments falling and subsequently shattering, resulting in difficulty in cleaning the affected tool. In this paper, we show that the two different fracture modes are related to plastic relaxation occurring, or not occurring, during the dwell time at high temperature.

2 Experimental method

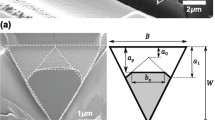

We have studied the different modes of wafer breakage from edge cracks artificially introduced into 200 mm diameter, (001) oriented, silicon wafers by 50N Vickers indentations located at \(90^\circ \), \(180^\circ \) and \(270^\circ \) with respect to the orientation notch and placed between 20 and \(120\,\upmu \hbox {m}\) from the bevel edge. Indentations were performed with a Mitutoyo AVK-C2 Hardness Tester (Garagorri et al. 2010). For loads below 50N and indents located typically 1mm from the bevel edge, four fold crack patterns resembling those described by Cook (2006) were observed. However, when the symmetry was broken by the proximity of the wafer edge break-out occurred predominantly on the wafer edge side of the indent, relaxing the strain and leaving one or more long cracks lying in the direction of the wafer centre. Provided that the crack length exceeded about 2 mm length and the indent was positioned within \(70 \, \upmu \hbox {m}\) of the bevel edge catastrophic fracture could occur in our rapid thermal annealing (RTA) system. The cracks were found to be good models of cracks introduced by damage associated with misaligned robotic handling tools.

The Si wafers used were dislocation-free silicon wafers purchased from Y Mart Inc, Palm Beach Gardens, Florida, USA. All wafers were within \(0.2^\circ \) of (100) orientation. The nominally defect-free, double side polished, p-type wafers had resistivity below 10 ohm mm, and were of thickness \(725 (\pm 25)\,\upmu \hbox {m}\). No edge defects were visible either under optical inspection or in XRDI images of the as-received wafers, which had been packed and shipped in standard cassettes.

All RTA experiments were conducted in a JetFirst 200C system, purchased from Qualiflow Therm-Jipelec. Details of the temperature-time profile during the annealing sequence, which was almost independent of the maximum temperature, can be found in Wittge et al. (2010). Two annealing schemes were used. In both cases, the heating time to \(1000\,{}^\circ \hbox {C}\) was 10 s and cooling achieved under forced gas convection. In the spike annealing procedure, cooling began immediately on reaching \(1000\,{}^\circ \hbox {C}\), while the plateau annealing involved holding the temperature at \(1000\,{}^\circ \hbox {C}\) for 60 s prior to cooling.

X-ray diffraction imaging was performed with the BedeScan\(^{\mathrm{TM}}\) tool (Bowen et al. 2003) at Jordan Valley Semiconductors (UK). MoKa (wavelength 0.0708 nm) radiation was used in the (Laue case) transmission geometry. The tool was operated in survey mode with a CCD detector of pixel size \(23.5 \, \upmu \hbox {m}\) and the adjacent three pixels were binned, giving an effective resolution of \(70.5 \, \upmu \hbox {m}\). The step size between each successive section topograph in the scan was six times the pixel size (\(141 \, \upmu \hbox {m}\)), giving a reasonable compromise between resolution and scan time. Under these conditions a complete scan of a 200 mm wafer took about 90 min.

3 Results

We have found that the fracture geometry during rapid thermal annealing (RTA) varied dramatically between wafers that had been subjected to spike annealing (Fig. 1a), where cooling began immediately on reaching the peak temperature, compared with those that had experienced plateau annealing (Fig. 1b), where wafers were held at the maximum temperature for 60 s. Spike annealed wafers exhibited crack patterns that started initially to run radially, but after a distance of typically 20–30 mm, turned and ran almost tangentially. Fracture did not occur on low index planes and was very irregular in direction (Fig. 1a).

On the other hand, those wafers subjected to plateau annealing fractured along \(\langle 110\rangle \) directions (Fig. 1b), corresponding to average cleavage on {111} planes, which have the lowest surface energy of the low index planes (Brun and Melkote 2009). There was a high degree of consistency in this attribution over all the wafers examined (Table 1).

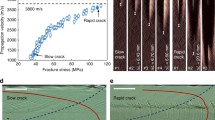

In all our RTA experiments, three thermocouples were placed on the rear surface of the wafer and when wafer fracture occurred, there was an abrupt and characteristic change in the temperature recorded, due to the disconnect between the wafer and the thermocouple (Fig. 2). A perturbation in at least two of the thermocouple readings at the same time (the perturbation of one could mean just failure of the thermocouple), typically a sudden temperature drop, was enough to detect the instant of breakage. We observed that, in the great majority of cases and where the wafer was properly located in the RTA tool, fracture did not occur during the heating of the wafer, but during the forced cooling process.

Yoo et al. (2002) observed an elastic deformation of wafers during temperature ramp up. The wafer shape began to deform as the temperature increased to a maximal deformation at a temperature of \(800\,{}^\circ \hbox {C}\). By the time a temperature of approx. \(950\,{}^\circ \hbox {C}\) had been reached, the wafer then became flat again, indicating that different stresses are introduced in the wafer during the RTA processing. Recently, Calvez et al. (2014) have used finite element (FE) modelling to predict critical propagation paths of cracks, initiated at the wafer edge, through silicon power devices subjected to accelerated thermal cycling tests. We have used finite element modelling of the elastic stresses within the wafer under realistic thermal conditions in the RTA furnace (Tanner et al. 2012; Garagorri et al. 2012) to identify the elastic stresses to which the initial cracks are subjected. Finite element modelling of the time-resolved thermal distribution in the RTA furnace was performed using the commercial software ABAQUS\(^\circledR \) version 6.10-EF1. The finite element model included a stainless steel processing chamber where the wafer is heated, and a very thin quartz window which separates the process chamber and the reactor from the heating source. A total of 118,859 elements have been necessary, where 5332 are associated with the axisymmetric mesh describing the substrate wafer. During heating, we observed that the tangential stresses at the wafer edge were always compressive, keeping the crack closed. On cooling, the tangential stress switched sign, opening the crack, enabling it to propagate radially. However, the stress in the centre of the wafer remained compressive and beyond about 20 mm, the crack would not propagate further in this direction. At this point it is energetically favourable for the crack to turn into a tangential direction as the radial stress remains tensile. This tensile stress opens the tangential crack, which propagates in an almost circumferential direction (Tanner et al. 2012). Figure 3 shows the boundary between the tensile and the compressive regimes in the FE simulations superimposed on the image of a broken wafer. The paths of the major circumferential cracks follow this boundary.

As evident in Table 1, all spike annealed wafers, except one low temperature anneal where the wafer unusually broke during the heating sequence, exhibited this circumferential cracking. However, despite excellent agreement between the predicted and observed fracture patterns in spike annealed wafers, no way could be found in which this purely elastic FE model of the wafer stresses could be adjusted to predict the existence of long straight cracks running along the \(\langle 110\rangle \) directions in plateau annealed wafers. We argue that the explanation of the two crack families lies in the presence of the substantial slip that occurs during plateau annealing providing relaxation of the compressive strains in the wafer centre.

X-ray diffraction imaging of spike annealed wafers has shown that slip is initiated at the wafer bevel but that it does not propagate more than about 1 mm into the wafer (Tanner et al. 2011) and is not usually evident in large area, low resolution X-ray diffraction images. However, XRDI of wafers subjected to plateau annealing, where the wafer is held for a 60 s at a temperature above the brittle to plastic transition, always revealed lengthy slip bands (Wittge et al. 2010; Garagorri et al. 2012) and usually showed slip steps visible optically on the surface. The slip band length followed an Arhenius exponential variation with maximum annealing temperature T (Garagorri 2014) and varied linearly with dwell time (Fig. 4), consistent with a constant dislocation velocity \(\upsilon (t,T)\) under the imposed stress field t of the form

and where E is the activation energy (measured to be \(2.1 \pm 0.2 \, \hbox {eV}\)), A and \(t_{0}\) are constants and m is close to unity and a function of T.

An example of the slip bands in such a wafer that fractured radially is given in Fig. 5. The image was taken in transmission mode with a BedeScan\(^{\mathrm{TM}}\) tool (Bowen et al. 2003). Fracture was initiated at a 50N Vickers indent at the top left of the wafer and propagated entirely in the \([1{\bar{1}}0]\) direction.

Inclusion of the effect of plastic relaxation was achieved by incorporating temperature dependent plasticity. The stress–strain curves were calculated from dislocation dynamics simulations using the open source Micromegas code. This software is a development of the work of Devincre et al. (2001). Dislocations are allowed to glide on all the 12 slip systems of {111} planes along \(\langle 110\rangle \) directions. Cross slip is not included in the simulations but as there is good correlation between slip band width and length in the diffraction images, the overall effect on the macroscopic strains will not be affected by this omission.

Finite element modelling of the stresses with inclusion of plastic deformation revealed a very different stress distribution as a function of annealing time. During the heating sequence the stresses were in the same sense as that predicted by the purely elastic model in that the tangential stress at the wafer edge was compressive, keeping the crack closed. As creep is not included in the FE model, the plastic relaxation will here be fully developed prior to cooling. On cooling, as for the purely elastic simulation, the tangential stress at the edge switched sign (Fig. 6c), opening the crack. However, in contrast to the purely elastic simulation, with inclusion of plastic relaxation, the radial stress near the edge of the wafer did not switch from compressive to tensile (Fig. 6a). As the tensile radial stress responsible for the change in crack orientation is no longer present, the crack continues to propagate. Because the {111} planes have the lowest surface energy (Tanaka et al. 2006), cleavage on these planes occurs preferentially and the brittle crack opens on this plane, resulting in a single, linear, fracture of the wafer which projects into the \(\langle 110\rangle \) direction in the plane of the wafer (Figs. 1b, 5). As cooling continues, the radial strain begins to change to tensile (Gorostegui-Colinas 2012) but not uniformly (Fig. 6b). The asymmetry of the resulting stress distribution is due to the crystallographic symmetry of the available slip systems being superimposed on the asymmetry associated with the heating elements in the furnace, resulting in a quite complex variation in the resolved shear stress as a function of angle around the wafer (Garagorri et al. 2012). At this stage, the tangential stress at the wafer edge is also predicted to switch back to being compressive (Fig. 6d) but by this time, the wafer will have fractured.

Evolution of radial [\(\hbox {s}_{11}\)] (a, b) and tangential hoop [\(\hbox {s}_{22}\)] (c, d) stresses during an anneal at \(800\,{}^\circ \hbox {C}\). a and c correspond to 2 s into cooling while b and d correspond to a time of 30 s after the start of cooling. Temperature dependent plasticity is used in the simulations. Units: Pa

The maximum stresses shown in Fig. 6 are of the order of 5–10 MPa and are determined by the thermal gradients in the RTA furnace used for the experiments. While these stresses are seemingly low, there is a large stress concentrator effect associated with the cracks we have introduced (and also for the cracks observed arising from handling tool damage, Tanner et al. 2012). Brede (1993) reported the fracture toughness \(K_{Ic}\) of silicon to be \(0.92 \, \hbox {MPa\,m}^{-0.5}\) at room temperature and in the ductile regime above \(800\,{}^\circ \hbox {C}\) as between 2.76 and \(7.36 \, \hbox {MPa\,m}^{-0.5}\). For the case of a plate with an edge crack of length a under tensile loading, the critical stress \(\sigma _{f}\) is given by

As exemplified in Tanner et al. (2012), the length of the critical cracks in our experiments was typically 10 mm and thus we find \(\sigma _{f} = 4.6\hbox {MPa}\) at room temperature and between 13.9 and 37MPa in the ductile regime above \(800\,{}^\circ \hbox {C}\). These values are of the order of magnitude found in the finite element simulations and we note that our experimental stress configuration is different to the case of a simple plate under tensile loading.

Samuels and Roberts (1989) studied the fracture of silicon initiated from indents under four point bending. They observed that below a critical temperature \(\hbox {T}_{\mathrm{c}}\), failure was by brittle fracture while above \(\hbox {T}_{\mathrm{c}}\) the failure was by ductile plastic yielding. They demonstrated that \(\hbox {T}_{\mathrm{c}}\) is a function of lattice hardness (doping level) and strain rate, their measured activation energy of \(2.1 \pm 0.1\hbox {eV}\) being in excellent agreement with our value, quoted above. While we do have evidence of plastic deformation during the plateau annealing, we have no evidence of ductile plastic yielding and none of the fractures show associated slip bands. The only examples of slip band nucleation at crack tips during plateau annealing are in wafers that did not fracture and the cracks did not propagate. Brittle fracture normally occurs during wafer cooling and we note that the FE simulations show that the temperature at the wafer edge is always lower than that at the centre. The thermocouples, which are located away from the wafer edge, will always give a reading higher than that at the edge. The evidence suggests that fracture from the edge crack predominantly occurs in the brittle regime but that during the plateau, the macroscopic plastic deformation relaxes the stress. We note that, when plastic relaxation does not occur, and the crack propagation is almost tangential, the crack path is not smooth and at a microscopic level the brittle crack path probably changes rapidly between low energy planes.

4 Conclusions

The very different fracture geometries in damaged silicon wafers following high temperature annealing under spike and plateau conditions are attributed to the presence of plastic relaxation during the plateau dwell time. This attribution of plastic deformation relaxing the stresses and resulting in linear cracking along the low index direction during plateau annealing, during which the wafer is held at a high temperature for 60 s, is consistent with the averaged dislocation velocity of \(0.24\,(\pm 0.02)\,\hbox {mm s}^{-1}\) presented in Fig. 4. In practice, a significant time is needed for the slip to occur and relax the thermal stresses. The lack of plastic relaxation in the spike anneal process arises from the fact that the wafer is not held for sufficiently long in the plastic regime above the brittle-ductile transition for the dislocations to travel far during that time.

References

Bowen DK, Wormington M, Feichtinger P (2003) A novel digital X-ray topography system. J Phys D Appl Phys 36:A17–23

Brede M (1993) The brittle-to-ductile transition in silicon. Acta Metall Mater 41:211–228

Brun XF, Melkote SN (2009) Analysis of stresses and breakage of crystalline silicon wafers during handling and transport. Solar Energy Mater Solar Cells 93:1238–1247

Calvez D, Roqueta F, Jacques S, Bechou L, Ousten Y, Ducret S (2014) Crack propagation modeling in silicon: a comprehensive thermomechanical finite-element model approach for power devices. IEEE Trans Compon Packag Manuf Technol 4:360–366

Chen PY, Tsai MH, Yeh WK, Jing MH, Chang Y (2009) Investigation of the relationship between whole–wafer strength and control of its edge engineering. Jpn J Appl Phys 48:126503

Chen PY, Tsai MH, Yeh WK, Jing MS, Chang Y (2010) Relationship between wafer edge design and its ultimate mechanical strength. Microelectron Eng 87:2065–2070

Cook RF (2006) Strength and sharp contact fracture of silicon. J Mater Sci 41:841–872

Devincre B, Kubin LP, Lemarchand C, Madec R (2001) Mesoscopic simulations of plastic deformation. Mater Sci Eng A 309:211

Garagorri J, Gorostegui-Colinas E, Elizalde MR, Allen D, McNally P (2010) Nanoindentation induced silicon fracture and 3D modelling. Anales de Mecánica de la Fractura 27:559–564

Garagorri J, Elizalde MR, Fossati MC, Jacques D, Tanner BK (2012) Slip band distribution in rapid thermally annealed silicon wafers. J Appl Phys 111:094901

Garagorri J (2014) Prediction of critical damage in silicon wafers during rapid thermal processing. Ph.D. Thesis, Universidad de Navarra, San Sebastian, Spain

Gorostegui-Colinas E (2012) Modelling of silicon behaviour for wafer fracture assessment during rapid thermal annealing. Ph.D. Thesis, Universidad de Navarra, San Sebastian, Spain

Samuels J, Roberts SG (1989) The brittle–ductile transition in silicon. I. Experiments. Proc R Soc Lond A 421:1–23

Tanaka M, Higashida K, Nakashima H, Takagi H, Fujiwara M (2006) Orientation dependence of fracture toughness measured by indentation methods and its relation to surface energy in single crystal silicon. Int J Fract 139:383–394

Tanner BK, Wittge J, Allen D, Fossati MC, Danilewsky AN, McNally P, Garagorri J, Elizalde MR, Jacques D (2011) Thermal slip sources at the extremity and beveledge of silicon wafers. J Appl Crystallogr 44:489–494

Tanner BK, Fossati MC, Garagorri J, Elizalde MR, Allen D, McNally PJ, Jacques D, Wittge J, Danilewsky AN (2012) Prediction of the propagation probability of individual cracks in brittle single crystal materials. Appl Phys Lett 101:041903

Wittge J, Danilewsky AN, Allen D, McNally PJ, Li ZJ, Baumbach T, Gorostegui–Colinas E, Garagorri J, Elizalde MR, Jacques D, Fossati MC, Bowen DK, Tanner BK (2010) X-ray diffraction imaging of dislocation generation related to microcracks in Si-wafers. Powder Diffr 25:99–103

Yoo WS, Fukada T, Yokoyama I, Kang K, Takahashi N (2002) Thermal behavior of large-diameter silicon wafers during high-temperature rapid thermal processing in single wafer furnace. Jpn J Appl Phys 41:4442–4449

Acknowledgments

Financial support was provided through the European Community FP7 STREP project SIDAM (Grant No. FP7-ICT-216382). Technical support from Kawal Sawhney and Igor Dolbnya at beamline B16 of the Diamond Light Source is gratefully acknowledged. Thanks are extended to SIDAM consortium members, particularly Keith Bowen, for valuable discussion and Matteo Fossati for assistance in data collection.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

Open Access This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

About this article

Cite this article

Tanner, B.K., Garagorri, J., Gorostegui-Colinas, E. et al. The geometry of catastrophic fracture during high temperature processing of silicon. Int J Fract 195, 79–85 (2015). https://doi.org/10.1007/s10704-015-0050-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10704-015-0050-1