Abstract

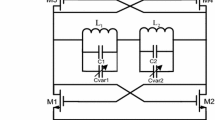

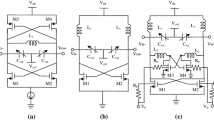

A 1 V low voltage, low power integer-N frequency synthesizer applied for 2.4 GHz wireless sensor network (WSN) applications is presented. The loop parameters of proposed charge pump phase lock loop frequency synthesizer is calculated and verified on the basis of continuous linear model. The proposed voltage controlled oscillator (VCO) consists of a PMOS cross-coupled transistor pair, a NMOS tail current source and a LC resonator. Common-mode 2nd harmonic filters are employed to improve loaded Q factor and suppress noise. LC resonator is optimized and switched capacitor array is used to lower AM–PM noise conversion. Fabricated in TSMC 0.18 μm CMOS process, the measured phase noise of VCO is −113.4 dBc/Hz@1 MHz, and −124.5 dBc/Hz@3.5 MHz while the frequency tuning range covers 4.56–5.32 GHz with 1 V voltage supply. The power dissipation is 2.3 mW and corresponding FOM is about −185 dBc/Hz. With other blocks of dividers, phase frequency detector, charge pump and auto frequency calibration, the die area of the whole fabricated frequency synthesizer is 1.33 mm2 with pads. With 1 V supply voltage and 9.1 mW power consumption, the measured phase noise of the frequency synthesizer is −121.9 dBc/Hz@1 MHz and −134.4 dBc/Hz@3.5 MHz respectively, and the reference spur is −44.5 dBc. The performance of the designed 1 V integer-N frequency synthesizer is suitable for IEEE 802.15.4/ZigBee based 2.4 GHz WSN applications.

Similar content being viewed by others

References

Shanan, H., Retz, G., Mulvaney, K., & Quinlan, P. (2009). A 2.4 GHz 2 Mb/s versatile PLL-based transmitter using digital pre-emphasis and auto calibration in 0.18 µm CMOS for WPAN. In IEEE international solid-state circuits conference-digest of technical papers, ISSCC (pp. 420–421).

Zhao, B., Yang, H., & Wang, H. (2012). A low-power fast-settling bond-wire frequency synthesizer with a dynamic-bandwidth scheme. In IEEE international symposium on circuits and systems (ISCAS) (pp. 1367–1370).

T. Instruments. (2007). CC2520: Second generation 2.4 GHz IEEE 802.15. 4/ZigBee-ready RF Transceiver.

Yu, S.-A., & Kinget, P. (2007). A 0.65 V 2.5 GHz fractional-N frequency synthesizer in 90 nm CMOS. In IEEE international solid-state circuits conference digest of technical papers, ISSCC (pp. 304–604).

Yuan, Q., Yang, H.-G., Dong, F.-Y., & Yin, T. (2008). Time borrowing technique for design of low-power high-speed multi-modulus prescaler in frequency synthesizer. In IEEE International Symposium on Circuits and Systems, ISCAS (pp. 1004–1007).

Italia, A., Ippolito, C. M., & Palmisano, G. (2012). A 1-mW 1.13–1.9 GHz CMOS LC VCO using shunt-connected switched-coupled inductors. IEEE Transactions on Circuits and Systems I: Regular Papers, 59, 1145–1155.

Lo, Y.-L., Yang, W.-B., Chao, T.-S., & Cheng, K.-H. (2009). Designing an ultralow-voltage phase-locked loop using a bulk-driven technique. IEEE Transactions on Circuits and Systems II: Express Briefs, 56, 339–343.

Craninckx, J., & Steyaert, M. S. (1995). A 1.8-GHz CMOS low-phase-noise voltage-controlled oscillator with prescaler. IEEE Journal of Solid-State Circuits, 30, 1474–1482.

Jang, S.-L., Huang, C.-J., Hsue, C.-W., & Chang, C.-W. (2010). A 0.3 V cross-coupled VCO using dynamic threshold MOSFET. IEEE Microwave and Wireless Components Letters, 20, 166–168.

Wohlmuth H.-D., & Kehrer, D. (2005). A 24 GHz dual-modulus prescaler in 90 nm CMOS. In IEEE international symposium on circuits and systems, ISCAS (pp. 3227–3230).

Krishna, M. V., Do, M. A., Yeo, K. S., Boon, C. C., & Lim, W. M. (2010). Design and analysis of ultra low power true single phase clock CMOS 2/3 prescaler. IEEE Transactions on Circuits and Systems I: Regular Papers, 57, 72–82.

Lacaita, A., Levantino, S., & Samori, C. (2007). Integrated frequency synthesizers for wireless systems. Cambridge: Cambridge University Press.

Shu, K., & Sánchez-Sinencio, E. (2010). CMOS PLL synthesizers: Analysis and design. New York: Springer Publishing Company, Incorporated.

Herzel, F., & Razavi, B. (1999). A study of oscillator jitter due to supply and substrate noise. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 46, 56–62.

Herzel, F., Osmany, S. A., & Scheytt, J. (2010). Analytical phase-noise modeling and charge pump optimization for fractional-N. IEEE Transactions on Circuits and Systems I: Regular Papers, 57, 1914–1924.

Wang, B., Hellums, J. R., & Sodini, C. G. (1994). MOSFET thermal noise modeling for analog integrated circuits. IEEE Journal of Solid-State Circuits, 29, 833–835.

Gardner, F. M. (2005). Phaselock techniques. New York: Wiley.

Jerng, A., & Sodini, C. G. (2005). The impact of device type and sizing on phase noise mechanisms. IEEE Journal of Solid-State Circuits, 40, 360–369.

Hegazi, E., Rael, J., & Abidi, A. (2005). The designer’s guide to high-purity oscillators. Berlin: Springer.

Bevilacqua, A., & Andreani, P. (2011). On the bias noise to phase noise conversion in harmonic oscillators using Groszkowski theory. In IEEE international symposium on circuits and systems (ISCAS) (pp. 217–220).

Berny, A. D., Niknejad, A. M., & Meyer, R. G. (2005). A 1.8-GHz LC VCO with 1.3-GHz tuning range and digital amplitude calibration. IEEE Journal of Solid-State Circuits, 40, 909–917.

Mazzanti, A., & Andreani, P. (2008). Class-C harmonic CMOS VCOs, with a general result on phase noise. IEEE Journal of Solid-State Circuits, 43, 2716–2729.

Huang, T.-H., & Tseng, Y.-R. (2008). A 1 V 2.2 mW 7 GHz CMOS quadrature VCO using current-reuse and cross-coupled transformer-feedback technology. IEEE Microwave and Wireless Components Letters, 18, 698–700.

Rong, S. & Luong, H. C. (2007). A 1 V 4-and-10 GHz transformer-based dual-band quadrature VCO in 0.18 μm CMOS. In IEEE custom integrated circuits conference, CICC (pp. 817–820).

Fu, C. T., & Luong, H. C. (2008). A 1 V CMOS quadrature LC VCO using diode coupling. In IEEE radio and wireless symposium (pp. 167–170).

Pan, Y., Chen, H., Shao, K., Huang, Y., & Hong, Z. (2010). A 6-GHz low-phase-noise voltage-controlled oscillator. In IEEE international 10th conference on solid-state and integrated circuit technology (ICSICT) (pp. 230–232).

Mohamed, S., Ortmanns, M., & Manoli, Y. (2008). Design of current reuse CMOS LC-VCO. In IEEE international 15th conference on electronics, circuits and systems, ICECS (pp. 714–717).

Mansuri, M., Liu, D., & Yang, C.-K. (2001). Fast frequency acquisition phase-frequency detectors for GSa/s phase-locked loops. In Proceedings of the 27th European solid-state circuits conference, ESSCIRC (pp. 333–336).

Hong, X., Zhiqun, L., Zhigong, W., Wei, L., & Li, Z. (2007). A charge pump design for low-spur PLL. Chinese Journal of Semiconductors-Chinese Edition, 28, 1988.

Leung, L. L. K., & Luong, H. C. (2008). A 1-V 9.7-mW CMOS frequency synthesizer for IEEE 802.11 a transceivers. IEEE Transactions on Microwave Theory and Techniques, 56, 39–48.

Yu, S.-A., & Kinget, P. (2009). A 0.65-V 2.5-GHz fractional-N synthesizer with two-point 2-Mb/s GFSK data modulation. IEEE Journal of Solid-State Circuits, 44, 2411–2425.

Vidojkovic, M., et al. (2012). A fully integrated 1.7–2.5 GHz 1 mW fractional-N PLL for WBAN and WSN applications. In IEEE radio frequency integrated circuits symposium (RFIC) (pp. 185–188).

Yan, H., Xiao, L., Haifeng, Z., Yinfang, X., & Waisum, W. (2010). A 0.8 V low power low phase-noise PLL. Journal of Semiconductors, 31, 085009.

Xizhen, Y., et al. (2012). A constant loop bandwidth fractional-N frequency synthesizer for GNSS receivers. Journal of Semiconductors, 33, 045007.

Acknowledgments

This paper is supported by the State Key Development Program for Basic Research of China (Grant No. 2010CB327404). And we are grateful for the encouraging discussions and technique assistances of the whole team in Institute of RF- & OE-ICs, Southeast University.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Fan, X., Tang, L., Wang, Y. et al. A 1 V 0.18 μm fully integrated integer-N frequency synthesizer for 2.4 GHz wireless sensor network applications. Analog Integr Circ Sig Process 82, 251–264 (2015). https://doi.org/10.1007/s10470-014-0459-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0459-x