Abstract

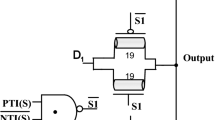

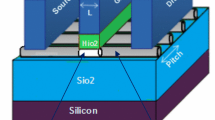

The Full Adder is one of the most important and basic units of mathematic circuits that is the basic structure of many complex systems. Moreover, serial and serial-parallel mathematic processes can be carried out faster and more operative error-detection and error-correction codes can be employed in ternary logic implementations. In this work, we presented a new high-performance Ternary Full Adder (TFA) based on Carbon Nanotube Field-Effect Transistor (CNTFET) technology. The proposed design is well-matched with the Carbon Nanotube Field-effect Transistor knowledge and ternary logic value. The presented structure reduces the delay of the Ternary Full Adder and has high driving capability. The proposed Ternary Full Adder is simulated at varying supply voltages and temperatures using different frequencies by the Synopsys HSPICE circuit simulator. Simulation results determine improvement in terms of delay and Power-Delay Product (PDP) in comparison with the state-of-the-art designs. Simulations show that the proposed Ternary Full Adder cell shows approximately more than 53 % improvement in PDP compared to its counterparts.

Similar content being viewed by others

References

J.T. Butler, The design of current mode CMOS multiple-valued circuits, in Multiple-Valued Logic VLSI. IEEE Computer Society Press Technology Series (IEEE Computer Society Press, Los Alamitos, 1991), pp. 130–138

P.C. Balla, A. Antoniou, Low power dissipation MOS ternary logic family. IEEE J. Solid-State Circuits 19, 739–749 (1984)

G. Cho, F. Lombardi, A novel and improved design of a ternary CNTFET-based cell, in GLSVLSI ’13, Proceedings of the 23rd ACM International Conference on Great Lakes Symposium on VLSI (2013), pp. 131–136

S.Y. Choi, W.B. Cho, J.H. Yim, S. Lee, D.-I. Yeom, G. Steinmeyer, V. Petrov, U. Griebner, Y.H. Ahn, K. Kim, H. Lim, F. Rotemund, Ultrashort pulse generation in bulk solid-state lasers using carbon nanotube saturable absorbers, in Proc. IEEE International Instrumentation and Measurement Technology Conference (2009), pp. 1–2

J. Deng, H.-S.P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—part I: model of the intrinsic channel region. IEEE Trans. Electron Devices 54, 3186–3194 (2007)

J. Deng, H.-S.P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—part II: full device model and circuit performance benchmarking. IEEE Trans. Electron Devices 54, 3195–3205 (2007)

S.A. Ebrahimi, P. Keshavarzian, S. Sorouri, M. Shahsavari, Low power CNTFET-based ternary Full Adder cell for nanoelectronics. Int. J. Soft Comput. Eng. 2(2), 291–295 (2012)

S. Ijiima, Catalytic growth of carbon microtubules with fullerene structure. Nature 354, 56–58 (1991)

P. Junsangsri, F. Lombardi, Design of a hybrid memory cell using memristance and ambipolarity. IEEE Trans. Nanotechnol. 12, 71–80 (2013)

A. Khatir, S. Abdolahzadegan, I. Mahmoudi, High speed multiple valued logic Full Adder using carbon nanotube field effect transistor. Int. J. VLSI Des. Commun. Syst. 2, 1–9 (2011)

S.C. Kleene, Introduction to Meta Mathematics (North-Holland, Amsterdam, 2009), pp. 332–340

R.D. Levine, F. Remacle, Realization of complex logic operations at the nanoscale. Architecture and design of molecule logic gates and atom circuits advances in atom and single molecule machines, pp. 195–220 (2013). doi:10.1007/978-3-642-33137-4_16

S. Lin, Y. Kim, F. Lombardi, Design of a ternary memory cell using CNTFETs. IEEE Trans. Nanotechnol. 11, 1019–1025 (2012)

M.H. Moaiyeri, R.F. Mirzaee, K. Navi, A. Momeni, Design and analysis of a high-performance CNFET-based Full Adder. Int. J. Electron. 99, 113–130 (2011)

M.H. Moaiyeri, R.F. Mirzaee, K. Navi, O. Hashemipour, Efficient CNTFET-based ternary Full Adder cells for nanoelectronics. Nano-Micro Lett. 3(1), 43–50 (2011)

P.L. McEuen, M. Fuhrer, H. Park, Single-walled carbon nanotube electronics. IEEE Trans. Nanotechnol. 1, 78–85 (2002)

K. Navi, S. Sayedsalehi, R. Farazkish, M. Rahimi Azghadi, J. Comp, A low-voltage and energy-efficient Full Adder cell based on carbon nanotube technology. Theor. Nanosci. 7, 1546 (2010)

A. Raychowdhury, K. Roy, Carbon nanotube electronics: design of high-performance and low-power digital circuits. IEEE Trans. Circuits Syst. 54, 2391–2401 (2007)

V. Schmidt, H. Riel, S. Senz, S. Karg, W. Riess, U. Gçsele, Realization of a silicon nanowire vertical surround-gate field-effect transistor. Small 2, 85–88 (2006)

K. Sridharan, S. Gurindagunta, V. Pudi, Efficient multiternary digit Adder design in CNTFET technology. IEEE Trans. Nanotechnol. 12, 283–287 (2013)

A. Srivastava, K. Venkatapathy, Design and implementation of a low power ternary Full Adder. VLSI Des. 4, 75–81 (1996)

Stanford University CNFET model Website. Stanford University, Stanford (2008). CA [Online]. Available http://nano.stanford.edu/model.php?id=23

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Keshavarzian, P., Sarikhani, R. A Novel CNTFET-based Ternary Full Adder. Circuits Syst Signal Process 33, 665–679 (2014). https://doi.org/10.1007/s00034-013-9672-6

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-013-9672-6