Abstract

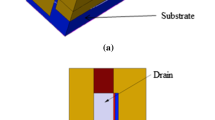

We present a rigorous surface-potential-based compact model of independent-gate asymmetric FinFETs enabled by solving several long-standing theoretical problems. The model is verified with TCAD simulations and is implemented in a standard circuit simulator. Simulation examples for both digital and analog circuits verify good model convergence and demonstrate the capabilities of new circuit topologies that can be implemented using independent-gate asymmetric FinFETs.

Similar content being viewed by others

References

Asenov, A., Slavcheva, G., Brown, A., Davies, J., Saini, S.: IEEE Trans. Electron Devices 48(4), 722 (2001)

Ortiz-Conde, A., García-Sánchez, F.J., Muci, J., Malobabic, S., Liou, J.J.: IEEE Trans. Electron Devices 54(1), 131 (2007)

Song, J., Yu, B., Yuan, Y., Taur, Y.: IEEE Trans. Circuits Syst. I 56(8), 1858 (2009)

Dessai, G., Dey, A., Gildenblat, G., Smit, G.D.J.: Solid-State Electron. 53(5), 548 (2009)

Taur, Y.: In: Gildenblat, G. (ed.) Compact Modeling: Principles, Techniques and Applications. Springer, Berlin (2010). Chap. 14

Cakici, T., Bansal, A., Roy, K.: In: Proc. IEEE Int. SOI Conf., pp. 21–22 (2003)

Pei, G., Kan, E.C.: IEEE Trans. Electron Devices 51(12), 2094 (2004)

Zhang, W., Fossum, J.G., Mathew, L., Du, Y.: IEEE Trans. Electron Devices 52(10), 2198 (2005)

Chiang, M.H., Kim, K., Chuang, C.T., Tretz, C.: IEEE Trans. Electron Devices 53(9), 2370 (2006)

Shrivastava, M., Baghini, M.S., Sachid, A.B., Sharma, D.K., Rao, V.R.: IEEE Trans. Electron Devices 55(11), 3274 (2008)

Tawfik, S.A., Kursun, V.: IEEE Trans. Electron Devices 55(1), 60 (2008)

Lu, H., Taur, Y.: IEEE Trans. Electron Devices 53(5), 1161 (2006)

Dessai, G., Gildenblat, G.: Solid-State Electron. 54(4), 382 (2010)

Sahoo, A., Thakur, P.K., Mahapatra, S.: IEEE Trans. Electron Devices 57(3), 632 (2010)

Gildenblat, G., Li, X., Wu, W., Wang, H., Jha, A., van Langevelde, R., Smit, G.D.J., Scholten, A.J., Klaassen, D.B.M.: IEEE Trans. Electron Devices 53(9), 1979 (2006)

Wu, W., Yao, W., Gildenblat, G.: Solid-State Electron. 54(5), 595 (2010)

Lu, D.D., Dunga, M., Lin, C.H., Niknejad, A.M., Hu, C.: In: IEDM Tech. Dig., pp. 565–568 (2007)

Liu, F., He, J., Fu, Y., Hu, J., Bian, W., Song, Y., Zhang, X., Chan, M.: IEEE Trans. Electron Devices 55(3), 816 (2008)

Dessai, G., Wu, W., Gildenblat, G.: IEEE Trans. Electron Devices 57(9), 2106 (2010)

Smit, G.D.J., Scholten, A.J., Curatola, G., van Langevelde, R., Gildenblat, G., Klaassen, D.B.M.: In: NSTI-Nanotech, vol. 3, pp. 520–525 (2007)

Lemaitre, L., Coram, G., McAndrew, C., Kundert, K.: In: Proc. BMAS, pp. 134–138 (2003)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Dessai, G., Wu, W., Bakkaloglu, B. et al. Compact model and circuit simulations for asymmetric, independent gate FinFETs. J Comput Electron 9, 103–107 (2010). https://doi.org/10.1007/s10825-010-0312-0

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-010-0312-0