Abstract

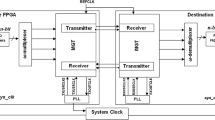

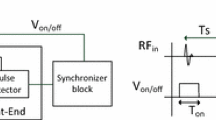

A simultaneous and reconfigurable multi-level RF-interconnect (MRI) for global network-on-chip (NoC) communication is demonstrated. The proposed MRI interface consists of baseband (BB) and RF band transceivers. The BB transceiver uses multi-level signaling (MLS) to enhance communication bandwidth. The RF-band transceiver utilizes amplitude-shift keying (ASK) modulation to support simultaneous communication on a shared single-ended on-chip global interconnect. A phase-locked loop (PLL) using a sub-harmonic multiply-by-10 injection-locked frequency multiplier is also designed to support a fully-synchronous NoC architecture. A differential voltage-controlled oscillator (VCO) used in a PLL creates an output frequency for a frequency range between 0.5 and 2.65 GHz signal. The multiply-by-10 ILFM generates 10 times higher frequency than the VCO output signal. Using the proposed multiply-by-10 ILFM can minimize the number of power-hungry frequency divider stages in a PLL feedback loop, resulting in improvement of the MRI power efficiency. The MLS-based BB and ASK-based RF band carry 10 Gb/s/pin and 4.4 Gb/s/pin, respectively. The proposed system is fabricated in a 65 nm CMOS process and achieves an energy efficiency of 2 pJ/b.

Similar content being viewed by others

References

Lee, K., Lee, S., & Yoo, H. (2006). Low-power network-on-chip for high performance SoC design. IEEE Transactions on VLSI Systems,14(2), 148–160.

Truong, D. N., Cheng, W. H., Mohsenin, T., Yu, Z., Jacobson, A. T., et al. (2009). A 167-processor computational platform in 65 nm CMOS. IEEE Journal of Solid-State Circuits,44(4), 1130–1144.

Lee, S. -K., Lee, S. -H., Sylvester, D., Blaauw, D. & Sim, J. -Y. (2013). A 95fJ/b current-mode transceiver for 10 mm on-chip interconnect. In Proceedings of IEEE ISSCC Digest of Technical Papers (pp. 262–263).

Höppner, S., Walter, D., Hocker, T., Henker, S., Hänzsche, S., et al. (2015). An energy efficient multi-Gbit/s NoC transceiver architecture with combined AC/DC drivers and stoppable clocking in 65 nm and 28 nm CMOS. IEEE Journal of Solid-State Circuits,50(3), 749–762.

Chen, M. -S., Chang, M. -C. F., & Yang, C. -K. K. (2015). A low-PDP and low-area repeater using passive CTLE for on-chip interconnects. In Symposium on VLSI Circuits (pp. C244–C245).

Mishra, A. K., Das, R., Eachempati, S., Iyer, R., Vijaykrishnan, N., & Das, C. R. (2009). A case for dynamic frequency tuning in on-chip networks. In Proceedings of IEEE/ACM International Symposium MICRO (pp. 292–303).

Mishra, A. K., Yanamandra, A., Das, R., Eachempati, S., Iyer, R., Vijaykrishnan, N., et al. (2011). Raft: A router architecture with frequency tuning for on-chip networks. Journal of Parallel and Distributed Computing,71(5), 625–640.

Huang, Y. S.-C., Chou, K. C.-K., & Chung-Ta, K. (2013). Application-driven end-to-end traffic predictions for low power NoC design. IEEE Transactions on VLSI Systems,21(2), 229–238.

Garg, S., Marculescu, D., Marculescu, R. & Ogras, U. (2009). Technology driven limits on DVFS controllability of multiple voltage-frequency island designs: A system-level perspective. In Proceedings of the ACM/IEEE DAC (pp. 818–821).

Lu, Z., & Yao, Y. (2017). Marginal Performance: Formalizing and Quantifying Power Over/Under Provisioning in NoC DVFS. IEEE Transactions on Computers,66(11), 1903–1917.

Dally, W. J. (2007). Enabling technology for on-chip interconnection networks. In Proceedings of the International Symposium on Networks-on-Chip (pp. 1–3).

Hansson, A., Goossens, K.,& Radulescu, V. (2005). A unified approach to constrained mapping and routing on Network-on-Chip architectures. In Proceedings of the IEEE/ACM/IFIP International Conference on Hardware/Software CODES+ISSS (pp. 75–80).

Lee, J., Ming-Shuan, C., & Huai-De, W. (2008). Design and comparison of three 20-Gb/s backplane transceivers for duobinary, PAM4, and NRZ data. IEEE Journal of Solid-State Circuits,43(9), 2120–2133.

Byun, G. S. & Navidi, M. M. (2015). A low-power 4-PAM transceiver using a dual-sampling technique for heterogeneous latency-sensitive network-on-chip. In IEEE Transactions on Circuits and Systems II: Express Briefs (Vol. 62, No. 6, pp. 613–617).

Jalalifar, M.,& Byun, G. S., (2014) An energy-efficient mobile PAM memory interface for future 3D stacked mobile DRAMs. In IEEE International Symposium on Quality Electronic Design, (pp. 675–680). Santa Clara, CA .

Jalalifar, M.,& G. S. Byun (2017). An energy-efficient mobile memory I/O interface using simultaneous bidirectional multilevel dual-band signaling. In IEEE Transactions on Circuits and Systems. II: Express Briefs (Vol. 64, No. 8, pp. 897–901).

Song, B., Kim, K., Lee, J., & Burm, J. (2013). A 0.18 μm CMOS 10-Gb/s Dual-Mode 10-PAM serial link transceiver. IEEE Transactions on Circuits and Systems I,60(2), 457–468.

Jalalifar, M., & Byun, G. -S. (2016). A 14.4 Gb/s/pin 230fJ/b/pin/mm multi-Level RF-interconnect for global network-on-chip communication. In IEEE Asian Solid-State Circuits Conference (ASSCC) (pp. 97–100).

Tam, S. -W. et al. (2009). A simultaneous tri-band on-chip RF-interconnect for future network-on-chip. In Symposium on VLSI Circuits (pp. 90–91).

Byun, G.-S., Kim, Y., Kim, J., Tam, S. W., & Chang, M.-C. F. (2012). An energy efficient and high-speed mobile memory I/O interface using simultaneous bi-directional dual (base+RF)-band signaling. IEEE Journal of Solid State Circuits,47(1), 117–130.

Kim, J., Kim, J. K., Lee, B. J., Kim, N., Jeong, D. K., & Kim, W. (2006). A 20-GHz phase-locked loop for 40-Gb/s serializing transmitter in 0.13-um CMOS. IEEE Journal of Solid-State Circuits,41(4), 899–908.

Richard, O., Siligaris, A., Badets, F., Dehos, C., Dufis, C., Busson, P., Vincent, P., Belot, D., & Urard, P. (2010). A 17.5-to-20.94 GHz and 35-to-41.88 GHz PLL in 65 nm CMOS for wireless HD applications. In Proceedings of the IEEE ISSCC Digest of Technical Papers (pp. 252–223).

Singh, U., & Green, M. M. (2005). High-frequency CML clock dividers in 0.13-µm CMOS operating up to 38 GHz. IEEE Journal of Solid-State Circuits,40(8), 1658–1661.

Lee, J., & Razavi, B. (2004). A 40-GHz frequency divider in 0.18-μm CMOS technology. IEEE Journal of Solid-State Circuits,39, 594–601.

Chen, Y.-T., Li, M.-W., Kuo, H.-C., Huang, T.-H., & Chuang, H.-R. (2012). Low-voltage K -band divide-by-3 injection-locked frequency divider with floating-source differential injector. IEEE Transactions on Microwave Theory and Techniques,60(1), 60–67.

Luo, T.-N., Bai, S.-Y., & Chen, Y.-J. E. (2008). A 60-GHz 0.13-µm CMOS divide-by-three frequency divider. IEEE Transactions on Microwave Theory and Techniques,56(11), 2409–2415.

Jalalifar, M., & Byun, G.-S. (2014). A K-band divide-by-five injection-locked frequency divider using a near-threshold VCO. IEEE Microw. Wireless Compon. Lett.,24(12), 881–883.

Wu, C.-Y., Chen, M.-C., & Lo, Y.-K. (2009). A phase-locked loop with injection-locked frequency multiplier in 0.18-µm CMOS for V-band applications. IEEE Transactions on Microwave Theory and Techniques,57(7), 1629–1636.

Reynolds, S. K., Floyd, B. A., Pfeiffer, U. R., Beukema, T., Grzyb, J., Haymes, C., et al. (2006). A silicon 60-GHz receiver and transmitter chipset for broadband communications. IEEE Journal of Solid-State Circuits,41(12), 2820–2831.

Floyd, B. A. (2008). A 16-18.8-GHz sub-Integer-N frequency synthesizer for 60-GHz transceivers. IEEE Journal of Solid-State Circuits,43(5), 1076–1086.

Wang, C.-C., Chen, Z., & Heydari, P. (2012). W-band silicon-based frequency synthesizers using injection-locked and harmonic triplers. IEEE Transactions on Microwave Theory and Techniques,60(5), 1307–1320.

Takano, K., Motoyoshi, M., & Fujishima, M. (2007). 4.8 GHz CMOS frequency multiplier with subharmonic pulse-injection locking. In IEEE Asian Solid-State Circuits Conference (pp. 336–339).

Chan, W. L., & Long, J. R. (2008). A 56-65 GHz injection-locked frequency tripler with quadrature outputs in 90-nm CMOS. IEEE Journal of Solid-State Circuits,43(12), 2739–2746.

Pin-Hao Feng; Shen-Iuan Liu. (2013). A current-reused injection-locked frequency multiplication/division circuit in 40-nm CMOS. IEEE Transactions on Microwave Theory and Techniques,61(4), 1523–1532.

Babaie, M., & Staszewski, R. B. (2013). A class-F CMOS oscillator. IEEE Journal of Solid-State Circuits,48(12), 3120–3133.

Chen, M.-C., & Wu, C.-Y. (2008). Design and analysis of CMOS subharmonic injection-locked frequency triplers. IEEE Transactions on Microwave Theory and Techniques,56(8), 1869–1878.

Leeson, D. B. (1966). A simple model of feedback oscillator noise spectrum. Proceedings of the IEEE,54(2), 329–330.

Temporiti, E., Albasini, G., Bietti, I., Castello, R., & Colombo, M. (2004). A 700-kHz bandwidth ΣΔ fractional synthesizer with spurs compensation and linearization techniques for WCDMA applications. IEEE Journal of Solid-State Circuits,39(9), 1446–1454.

Rhee, W. (1999). Design of high-performance CMOS charge pumps in phase-locked loops. In Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS) (pp. 545–548).

Jalalifar, M., & Byun, G.-S. (2013). Near-threshold charge pump circuit using dual feedback loop. Electronics Letters,49(23), 1436–1438.

Xu, W., & Friedman, E. G. (2002). Clock feedthrough in CMOS analog transmission gate switches. In Annual IEEE International ASIC/SOC Conference (pp. 181–185).

Allen, P. E., & Douglas, R. H. (2002). CMOS analog circuit design. Oxford: Oxford University Press.

Young, Ian A., Greason, Jeffrey K., & Wong, Keng L. (1992). A PLL clock generator with 5 to 110 MHz of lock range for microprocessors. IEEE Journal of Solid-State Circuits,27(11), 1599–1607.

Eken, Y. A., & Uyemura, J. (2004). A 5.9-GHz voltage-controlled ring oscillator in 0.18-μm CMOS. IEEE Journal of Solid-State Circuits,39(1), 230–233.

Jalalifar, M., & Byun, G. S. (2016). A wide range CMOS temperature sensor with process variation compensation for on-chip monitoring. IEEE Sensors Journal,16(14), 5536–5542.

Levantino, S., Samori, C., Bonfanti, A., Gierkink, S. L. J., Lacaita, A. L., & Boccuzzi, V. (2002). Frequency dependence on bias current in 5 GHz CMOS VCOs: impact on tuning range and flicker noise upconversion. IEEE Journal of Solid-State Circuits,37(8), 1003–1011.

Gharibdoust, K., Tajalli, A., & Leblebici, Y. (2016). A 4 × 9 Gb/s 1 pJ/b Hybrid NRZ/Multi-Tone I/O With Crosstalk and ISI Reduction for Dense Interconnects. IEEE Journal of Solid-State Circuits,51(4), 992–1002.

Du, Y., Cho, W. H., Huang, P. T., Li, Y., Wong, C. H., Du, J., et al. (2017). A 16-Gb/s 14.7-mW tri-band cognitive serial link transmitter with forwarded clock to enable PAM-16/256-QAM and channel response detection. IEEE Journal of Solid-State Circuits,52(4), 1111–1122.

Acknowledgement

This work was supported by the Inha University Research Grant under Grant INHA-00000.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Jalalifar, M., Byun, GS. An energy-efficient multi-level RF-interconnect for global network-on-chip communication. Analog Integr Circ Sig Process 102, 131–143 (2020). https://doi.org/10.1007/s10470-019-01459-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01459-1