Abstract

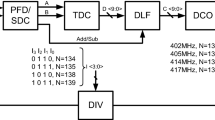

This paper presents a high-frequency wide tuning range all digital phase locked loop (ADPLL) designed using a 90 nm CMOS process with 1.2 V power supply. It operates in the frequency range of 1.9–7.8 GHz. The ADPLL uses a wide frequency range digital controlled oscillator (DCO) and a two stage acquisition process to obtain the fast lock time. The operation of the ADPLL includes both a frequency acquisition state and a phase acquisition state. A novel architecture is implemented which includes a coarse acquisition stage to obtain a monotonically increasing wide frequency range DCO for frequency acquisition and a fine control stage to achieve resolution of 18.75 kHz for phase tracking. Design considerations of the ADPLL circuit components and implementation using Cadence tools are presented. Spectre simulations demonstrate a peak-to-peak jitter value of <15 ps and a root mean square jitter value of 4 ps when locked at 5.12 GHz. The power consumption at 7.8 GHz is 8 mW and the frequency hopping time is 3.5 μs for a 3.2 GHz frequency change. Spectre simulations demonstrate ADPLL convergence to 5.12 GHz for the typical, fast, and slow process corners to support robust performance considering process variations.

Similar content being viewed by others

References

Chen, X., Yang, J., & Shi, L. X. (2011). A fast locking all-digital phase-locked loop via feed-forward compensation technique. IEEE Transactions on Very Large Scale Integration System, 19(5), 857–868.

Lee, D. C., Kim, K. Y., Min, Y. J., Park, J., & Kim, S. W. (2011). A jitter and power analysis on DCO. IEEE Transactions on Circuits and Systems, 58(9), 560–564.

Wu, C. T., Shen, W. C., Wang, W., & Wu, A. Y. (2010). A two-cycle lock-in time ADPLL design based on a frequency estimation algorithm. IEEE Transactions on Circuits and Systems, 57(6), 430–434.

Ren, S., Emmert, J., & Siferd, R. (2011). Design and performance of a robust 180 nm CMOS standalone VCO and the integrated PLL. Analog Integrated Circuits and Signal Processing, 68, 285–298.

Staszewski, R. B. (2011). State-of-the-art and future directions of high-performance all-digital frequency synthesis in nanometer CMOS. IEEE Transactions on Circuits and Systems, 58(7), 1497–1510.

Mokhtari, E., & Savvan, M. (2003). CMOS high-resolution all-digital phase-locked loop. Proceedings of IEEE International Symposium on Micro-Nano Mechatronics and Human Science, 12, 221–224.

Temporiti, E., Weltin-Wu, C., Baldi, D., Tonietto, R., & Svelto, F. (2009). A 3 GHz fractional all-digital PLL with a 1.8 MHz bandwidth implementing spur reduction techniques. IEEE Journal of Solid-State Circuits, 44(3), 824–834.

Lee, J., & Kim, B. (2000). A low-noise fast-lock phase-locked loop with adaptive bandwidth control. IEEE Journal of Solid-State Circuits, 35(8), 1137–1145.

Hung, C.-M., Staszewski, R. B., Barton, N., Lee, M.-C., & Leipold, D. (2006). A digitally controlled oscillator system for SAW-less transmitters in cellular handsets. IEEE Journal of Solid-State Circuits, 41(5), 1160–1170.

Pittorino, T., Chen, Y., Neubauer, V., Vollenbruch, U., Mayer, T., & Maurer, L. (2006). A first dual-mode RF fully digitally controlled oscillator in 0.13 μm CMOS. Proceedings of 36th European Microwave Conference, 9, 79–82.

Wang, S., Quan, J., Luo, R., Cheng, H., & Yang, H. (2007). A noise reduced digitally controlled oscillator using complementary varactor pairs. Proceedings of IEEE International Symposium on Circuits and Systems, 5, 937–940.

Oh, D.-H., Kim, D.-S., Kim, S., Jeong, D.-K., & Kim, W. (2007). A 2.8 Gb/s all-digital CDR with a 10b monotonic DCO. Proceedings of IEEE International Solid-State Circuits Conference, Digest of Technical Papers, 2, 222–223.

Rylyakov, A. V., Tierno, J. A., English, G. J., Friedman, D., & Megheli, M. (2007). A wide power-supply range (0.5 V-to-1.3 V) wide tuning range (500 MHz-to-8 GHz) all-static CMOS ADPLL in 65 nm SOI. Proceedings of IEEE International Solid-State Circuits Conference, Digest of Technical Papers, 2, 172–173.

Yu, G., Wang, Y., Yang, H., & Wang, H. (2010). Fast-locking all-digital phase-locked loop with digitally controlled oscillator tuning word estimating and presetting. IET Circuits, Devices and Systems, 4(3), 207–217.

Lin, S.-Y., & Liu, S.-I. (2009). A 1.5 GHz all-digital speed-spectrum clock generator. IEEE Journal of Solid-State Circuits, 44(11), 3111–3119.

Choi, K.-H., Shin, J.-B., Sim, J.-Y., & Park, H.-J. (2009). An interpolating digitally controlled oscillator for a wide-range all-digital PLL. IEEE Transactions on Circuits and Systems, 56(9), 2055–2063.

Sheng, D., Chung, C.-C., & Lee, C.-Y. (2006). An all-digital phase-locked loop with high-resolution for SoC applications. Proceedings of International Symposium on VLSI Design, Automation and Test, 4, 1–4.

Abidi, A. A. (2006). Phase noise and jitter in CMOS ring oscillators. IEEE Journal of Solid-State Circuits, 41(8), 1803–1816.

Analog Device Data Sheet (2007). High resolution 6 GHz fractional-N frequency synthesizer ADF4157, pp. 9.

Kundert, K. (2006). Predicting the phase noise and Jitter of PLL-based frequency synthesizers. Mountain View: Designer’s Guide Consulting, Inc.

Chen, J., Fang, S.-H., & Chen, X. (2008). A novel DCPLL with small-area and low-power DCO for SoC applications. In Proceedings of the 9th international conference on solid-state and integrated-circuit technology, Beijing (pp. 1867–1870).

Kim, D.-S., Song, H., Kim, T., Kim, S., & Jeong, D.-K. (2010). A 0.3–1.4 GHz all-digital fractional-N PLL with adaptive loop gain controller. IEEE Journal of Solid-State Circuits, 45(11), 2300–2311.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Muppala, P., Ren, S. & Lee, G.YH. Design of high-frequency wide-range all digital phase locked loop in 90 nm CMOS. Analog Integr Circ Sig Process 75, 133–145 (2013). https://doi.org/10.1007/s10470-013-0043-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-013-0043-9