Abstract

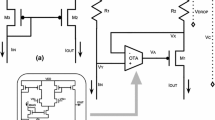

Analog MOS circuits are becoming increasingly sophisticated in terms of checking and correcting themselves. Self-correcting, self-compensating, or self-calibrating techniques eliminate errors traditionally associated with analog circuits. For real-time applications, however, it is rather difficult to achieve validation of the data generated from analog-to-digital (A/D) converters in the presence of faulty switching element(s). Conventionally, the validation is accomplished by using a high resolution and high accuracy D/A converter and a window comparator; i.e., the validation must highly depend on the reliability of both the D/A converter and the window comparator. In this paper, a novel current-mode A/D converter design with concurrent error detection (CED) capability is presented. The A/D converter does not need well-matched components and high-gain amplifiers. Results show that the proposed design can detect all the transient faults and most of the permanent faults. The proposed design allows users to easily switch to the normal operation mode where CED capability is not used, without causing any performance degradation.

Similar content being viewed by others

References

Y.P. Tisividis, “Analog MOS integrated circuits—certain new ideas, trends, and obstacles,IEEE J. Solid-State Circuits, Vol. SC-22, pp. 317–321, June 1987.

R. Poujois, B. Baylac, D. Barbier, and J.M. Ittel, “Low-level MOS transistor amplifier using storage elements,”IEEE ISSCC Dig. Tech. Papers, pp. 152–153, 1973.

Y.P. Tisvidis, M. Banu, and J.F. Khoury, “Continuous-time MOSFET-C filters in VLSI,”IEEE J. Solid-State Circuits, Vol. SC-21, pp. 15–30, Feb. 1986.

H.T. Yung and K.S. Chao, “An error-compensation A/D conversion technique,”IEEE Trans. Circuits Systems, Vol. 38, pp. 187–195, Feb. 1991.

Analog Devices,Analog-Digital Conversion Handbook, Prentice-Hall: Englewood Cliffs, NJ, 1986.

J.A. Abraham and V.K. Agarwal, “Test generation for digital systems,” inFault-Tolerant Computing, Theory and Techniques (D.K. Pradhan, ed.), Prentice-Hall: Englewood Cliffs, NJ, 1986.

J.H. Patel and L.Y. Fung, “Concurrent error detection in ALUs by recomputing with shifted operands,”IEEE Trans. Comput., Vol. C-31, pp. 589–595, July 1982.

Y.H. Choi, S.H. Han, and M. Malek, “Fault diagnosis of reconfigurable systolic arrays,” inProc. Conf. Computer Design: VLSI in Computers and Processors (ICCD '84), pp. 451–455, 1984.

R.K. Gulati and S.M. Reddy, “Concurrent error detection VLSI structures,” inProc. Int. Conf. Computer Design: VLSI in Computers and Processors (ICCD '86), pp. 488–491, 1986.

S.-W. Chan, S.S. Leung, and C.L. Wey, “Systematic design strategy for concurrent error diagnosable iterative logic arrays,”IEE Proc. E, Vol. 135, No. 2, pp. 87–94, March 1988.

S.-W. Chan and C.L. Wey, “The design of concurrent error diagnosable systolic arrays for band-matrix multiplication,”IEEE Trans. CAD Integrated Circuits Systems, Vol. CAD-7, No. 1, pp. 21–37, Jan. 1988.

D.A. Reynolds and G. Metze, “Fault detection capabilities of alternating logics,”IEEE Trans. Comput., Vol. C-27, pp. 1093–1098, Dec. 1978.

C.L. Wey, “Concurrent error detection in array dividers by alternating input data,” inProc. Int. Conf. Computer Design: VLSI in Computers and Processors (ICCD '91), pp. 114–117, Oct. 1991.

B. Wilson, “Recent developments in current conveyors and current-mode circuits,”IEE Proc., Vol. 137, Part G, No. 2, pp. 63–77, April 1990.

D.G. Nairn and C.S. Salama, “A ratio-independent algorithmic analog-to-digital converter combining current mode and dynamic techniques,”IEEE Trans. Circuits Systems, Vol. 37, No. 3, pp. 319–325, March 1990.

C.L. Wey and S. Krishnan, “Current-mode divide-by-two circuit,”Electron. Lett., Vol. 28, No. 9, pp. 820–822, April 1992.

T.R.N. Rao and E. Fujiwara,Error-Control Coding for Computer Systems, Prentice-Hall: Englewood Cliffs, NJ, 1989.

S. Sahli, M.S. thesis, Department of Electrical Engineering, Michigan State University.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Wey, CL., Krishnan, S. & Sahli, S. Design of concurrent error detectable current-mode A/D converters for real-time applications. Analog Integr Circ Sig Process 4, 65–74 (1993). https://doi.org/10.1007/BF01240680

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF01240680